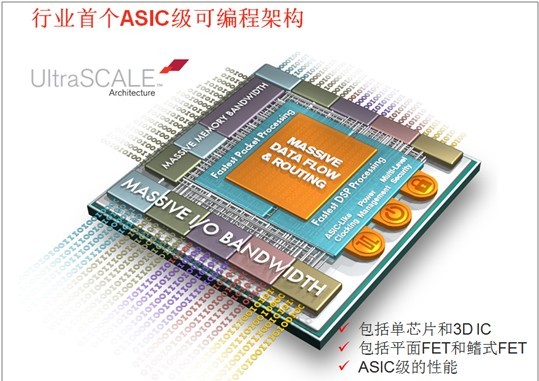

今天,Xilinx公司宣布推出了行业首个ASIC级可编程架构UltraScale,并且其首款20nm All Programmable器件开始投片[1]。Xilinx官方称:“20nm UltraScale器件相对竞争产品,提前一年实现1.5至2倍的系统级性能和可编程系统集成度。”

笔者认为Xilinx这次发布的创新看似两个:1.20nm工艺, 2.工艺采用ASIC级可编程架构UltraScale。但是,真正有震撼力的是UltraScale。

为何“相比竞争产品,提前一年……”

据我们所知,一家名叫Achronix的FPGA小公司,依靠Intel的代工后盾,早在今年初就交付了22nm Tri-Gate晶体管FPGA,20/22nm工艺方面可谓推出第一人。而Altera在Achronix宣布22nm几天后就放出话,正在和Intel合作14nm Tri-Gate FPGA,明年就可出货,可谓未来第一人。

在此背景下,Xilinx有底气说出“第一”,肯定不是工艺优势,而是杀手锏——“UltraScale”。

Xilinx还真不愧为“赛灵思”!创新性地提出UltraScale架构,把上述困扰一举搞定。那么,性能咋提高了40%?笔者理解,说白了,就是在线网密集的城市里,再专门铺设一些高速路(这些固定的路线就是被称为"ASIC级"的原因吧!)。而功耗等问题主要由Xilinx和老搭档TSMC搞定。

1. Xilinx全球副总裁、亚太区执行总裁汤立人称,ASIC级UltraScale架构在布线、类似ASIC的时钟分布、增加CLB逻辑、控制集功能以及关键路径优化方面具有明显的优势,不仅可以解决系统总吞吐量扩展和时延方面的局限性,而且还能直接突破高级节点上的头号系统性能瓶颈,即互连问题。

感悟:真要“赛灵思”!

这话说起来轻巧,在数千万、上亿门的FPGA上,高速路也不是那么好建的。看看咱们的城市,辛勤的建设者们要花费n年、以亿元为单位的投资才能实现。笔者估计,Xilinx早已储备了这种技术,只是到了万不得已才会用出来,这也防止竞争对手在短时间内效仿。

多年来,Xilinx并不是简单地将传统FPGA移植到新的工艺节点上,而是设计出了大量FPGA创新技术,例如在28nm制程时推出首款商用All Programmable 3D IC、Zynq SoC和Vivado设计套件。

这种创新意识和创新精神,真值得我们学习和借鉴!

参考文章:

[1]Xilinx首个ASIC级可编程架构20nm All Programmable器件开始投片.(2013-7-11).http://www.eepw.com.cn/article/147389.htm

[2]Xilinx UltraScale架构—业界首款ASIC级All Programmable架构.(2013-7-10).http://www.eepw.com.cn/article/147355.htm

[3]Xilinx首个ASIC级UltraScale可编程架构-常见问题.(2013-7-11).http://www.eepw.com.cn/article/147390.htm

---------------

新浪微博:王莹_迎九http://weibo.com/u/1723735885

QQ:1433566798

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。