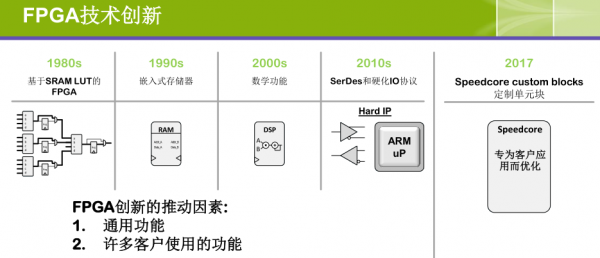

纵观FPGA的技术创新史,传统FPGA制造商所关注的提供通用的可编程功能,例如上世纪80年代提供基于SRAM LUT的功能,90年代推出嵌入式RAM存储器,2000年代推出加强数学运算的DSP,2010年代加入SerDes和硬化的I/O协议。他们的共同特点是通用性强,因此一块FPGA可以卖给不同的客户,但是缺少定制性。

图:FPGA的技术创新史

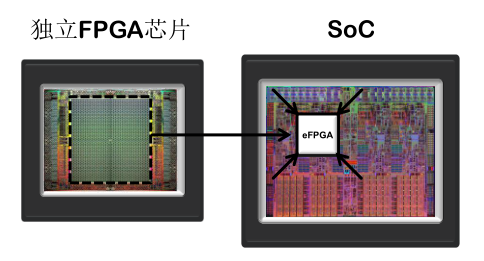

为此,Achronix公司不久前推出了定制化的custom blocks(定制单元块)。名为Speedcore Custom Blocks的IP新产品可加速数据密集的人工智能(AI)/机器学习、5G移动通信、汽车先进驾驶员辅助系统(ADAS)、数据中心和网络应用。该公司的Speedcore嵌入式FPGA(eFPGA)IP产品已于2016年10月问世,特点是可以把FPGA嵌入到ASIC或者SoC之中。

图:独立FPGA与嵌入式FPGA(eFPGA)的版图布局

eFPGA推高Achronix营收

Achronix公司在京新闻发布会上,公司市场营销副总裁Steve Mensor向电子产品世界记者介绍了这款产品的推出背景及新产品架构。

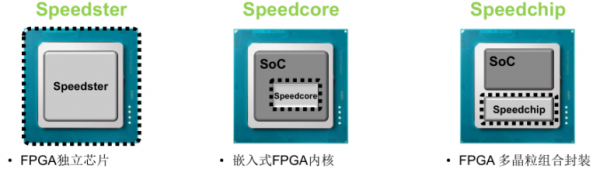

Archronix目前有三个产品系列:独立芯片,嵌入式FPGA内核,和客户的芯片进行组合封装(如下图)。

图:Achronix的FPGA产品线

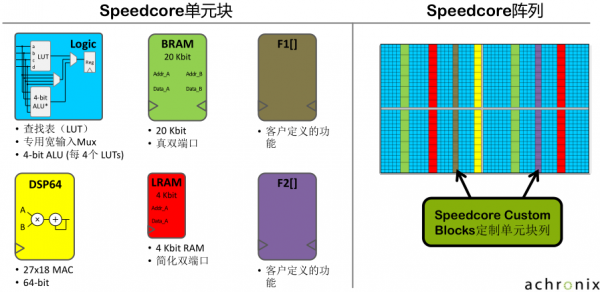

Speedcore Custom Blocks的组织方式和传统的DSP、RAM和logic的组织方式是一致的,也是以列形式放置在架构中。数量多少可以灵活调节,如下图的棕色和紫色单元块是Speedcore Custom Blocks。

图:Speedcore的列形式组织

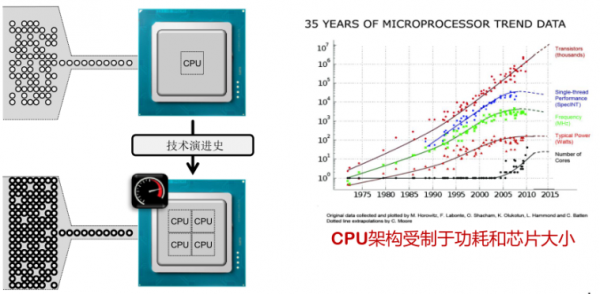

为了应对计算能力的急速增长,会对硬件的性能提出更新的需求。过去传统CPU/冯.诺依曼架构,计算能力的提升是通过提指令、取数据的串行方式来实现。为了提高性能,只能增加CPU/核的数量,提高单位CPU/核的频率。但这种方式的缺陷是会在一定的物理限制(诸如功耗和面积)下会达到极限,在某一拐点上增长不会按照预期进行了(如下图)。

图:CPU的演进史

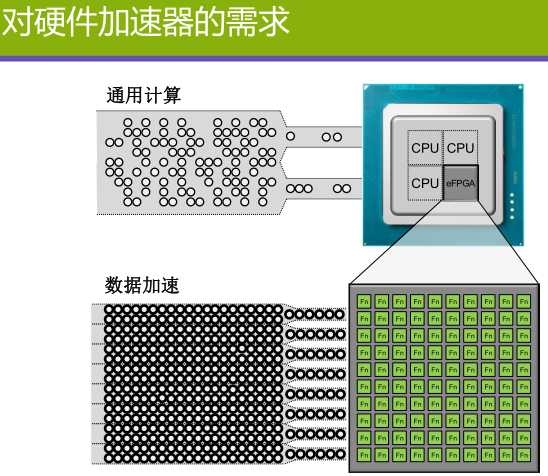

为了克服这种增加CPU/core的挑战,传统行业提出了异构计算,由外部的硬件加速来协助CPU进行数据处理。传统的CPU可以作为控制流或进行较为简单的计算,硬件加速器可以并行处理大量计算。这种组合可以大幅提升计算速度。例如下图的eFPGA就可实现硬件加速器功能。

图:硬件加速器的应用

为何eFPGA比标准FPGA更高效?

主要有如下三大原因。

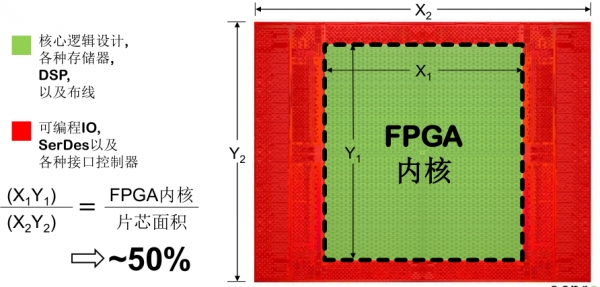

*原因1。如下图,传统FPGA构架中,周围的红色边框放置可编程I/O、高速SerDes及各种接口控制器,这些会占有30%~40%面积。如果做成嵌入式FPGA,这些面积可以省掉。下图公式展示的FPGA和片芯面积的比例。

图:核心电路与边缘电路的比例

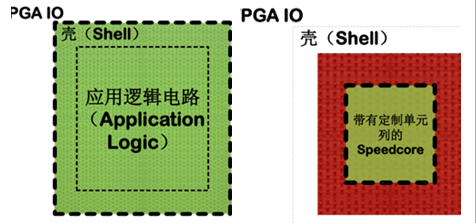

在此研究中,这些shell一旦固定到应用中,这些可编程不能被可编程(即固定下来了)。另外,核心应用是会改变的。因此如果拿掉shell,会节省44%的面积。

图:如果去掉shell,会节省近一半的面积(注:左右两图的左上角均为“FPGA IO”)

*原因3。在把shell剥去的基础上,又增加了自定义的custom block,这是由客户自定义的,分布在speedcore架构之中,有了这种custom block,面积会缩小75%,同时有更低功耗和更高的性能。

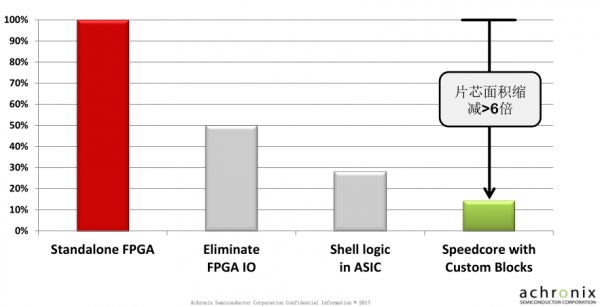

基于以上三个原因,即裁剪了FPGA的可编程I/O,shell资源去掉,另外提高了custom block,因此片芯面积大大缩减(如下图)。

图:与独立FPGA相比,把Speedcore的三个优势

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。