三年前的预言将兑现

记得2007年的10月,Xilinx的CTO(首席技术官)Ivo Bolsens来华访问时,向我们展望了Xilinx FPGA的未来,他预言未来几年3D封装FPGA将出现。

时光荏苒,今天——2010年10月28日,Xilinx在京再次召开新闻发布会,向业界宣布其FPGA堆叠硅片互联技术(SST),并称一年后28nm的四FPGA硅片封装产品将上市[1]。

Xilinx亚太区执行总裁 质量管理和新产品导入全球资深副总裁 汤立人

超越“摩尔定律”

前几天,笔者刚刚写了一篇“FPGA仅仅追求门的时代结束了”,认为一些FPGA厂商在增加嵌入式处理和数模混合信号方向努力。Xilinx为何在此时使FPGA的门数大为增加?因为按照摩尔定律及超越摩尔定律,晶体管密度每18个月翻番,按说Xilinx明年初诞生的28nm FPGA已经符合此规律,为何超越这些定律(more-than-moore)了![2]

Xilinx亚太市场与应用总监张宇清称,此举主要想占领更大型ASIC市场。FPGA 3D封装产品为少数处于领先地位的客户要求Xilinx在产品推出后尽快为他们提供批量生产所需的最大型FPGA器件。例如通信市场要求FPGA集成数十个串行收发器以及更多互联逻辑和block RAM,以支持高级数据处理和流量管理,同时外形尺寸和功耗还应不超过目前水平。

汤立人进一步解释说,首先28nm FPGA在刚出来的时候,由于良率不高,因此高密度系列FPGA产量一时上不去,致使高密度FPGA不能在市场上立即被广为应用(如下图),因此用4硅片低密度FPGA组合成高密度产品。

但笔者注意到新闻稿上有一句有趣的一句话:“Xilinx 28nm 7系列FPGA目标设计平台所能满足的资源需求,是最大单芯片FPGA所能达到的2倍。”

Xilinx的3D封装明明是集成了4个硅片,为何是“最大单芯片FPGA”的2倍?这句话怎么理解?笔者猜测,这“最大单芯片FPGA”不是Xilinx的,而是其竞争对手——Altera的!

因此,Xilinx想超越的不是摩尔定律,而是Altera!

上图是Xilinx单方绘制的More than Altera图。图中28nm的蓝柱是Altera 28nm工艺时,带serdes(收发器)FPGA预期可达到的性能("超越摩尔定律");红柱是Xilinx 3D封装可达到的性能。张宇清解释了新闻稿中的2倍为何变为上图2.8倍:Altera最大FPGA是1.1M LE(逻辑单元),最大带serdes的FPGA密度相对小一些;Xilinx一年后将推出的第一款3D产品Virtex-7 2000T容量可达200万LE。

那么,Altera是否也会如法炮制,推出4硅片3D封装FPGA,盖过Xilinx?!

3D封装的优势

为了对得起Xilinx的招待午餐,还是先暂且停下这个话题,从3D封装及Xilinx如何实现的展开吧……

业界普遍认为,平面封装和3D封装是未来超越摩尔定律、增大芯片密度的主要方法之一。

Xilinx现在推出,最实在的是想取代四个单片的FPGA设计,称可以大大简化设计,尤其是高速通信中敏感的信号延迟(时序闭合)问题。

至于价格,Xilinx张宇清来了一个脑筋急转弯:在成本方面3D封装的肯定比四个单片FPGA要低。不过,产品的定价是以价值为何核心的,主要看能给客户带来什么样的价值。

Xilinx亚太市场与应用总监张宇清

很多美国信奉麦肯锡的value-based价值理念。

3D封装展示

无论动机如何,定价如何,事实是Xilinx推出了3D封装。让我们暂且抛开各种利益和市场纠葛,欣赏一下Xilinx的3D封装吧!

从剖面图可看到,四个芯片将紧密地并列在一起。与2D封装不同的是,下图中间蓝色的部分是Si Interposer(硅中间层),里面有上万条金属线,合计10个金属层(TSMC称之为被动元件层),TSMC生产,工艺65nm。由此可见,是FPGA芯片、硅中间层上下堆叠起来的,区别于SoC(系统芯片)和SiP(系统封装)。

Xilinx称其研发了蓝色:硅中介层和封装设计,并进行封装部件的最后测试。尤其硅中介层的硅通孔(TSV)技术是该公司的核心技术。

汤立人称Xilinx之所以能够3D,是因为其独特的FPGA架构。从上面俯视图可见,为了实现3D,几年前Xilinx已在架构上进了规划,是Xilinx FPGA是4列(slice,片)结构,Slice间超过1万个过孔走线,每线的时延为1ns(纳秒)。相比之下,在PCB(印制电路板)、MCM(多芯片模块,内部通常有PCB)走线的时延一般是ps(皮秒)级的。

通常认为,3D封装应该叠加起来,而且应该是各种芯片的叠加,例如存储器、处理器等。但Xilinx把自己的FPGA 3D起来,已经是一种可喜的创新。汤立人解释说之所以没有FPGA叠加,因为FPGA功耗较大,并列有利于散热。而像存储器等器件由于功耗不高,可以向上叠加。

评 论

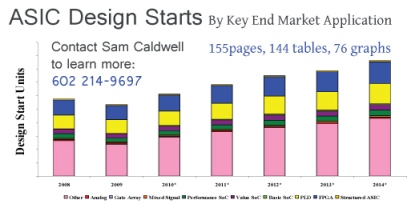

此番,通过3D封装,Xilinx又燃起了FPGA追求高逻辑单元/门数的战火,目标直指大型ASIC。据Semico Reserch分析,当前ASIC的开工率有所上升[3]。此回超越摩尔定律,Xilinx是否会旗开得胜,还有待市场检验。

但是,未来,预计在摩尔定律即将完成使命之前(11.7nm物理门极限),其他FPGA厂商也会陆续开始3D封装。Xilinx尽管称其独特架构特别适合3D封装,但其他竞争对手也不垃圾啊,一定也会有高招解决的。

预计FPGA厂商在3D封装的基础上,将来也会往里填充一些新技术/功能,诸如嵌入式处理、存储器、模拟等,以满足各种目标平台的应用。按照此推理,如果我是Xilinx的领导,我就买下Microsemi这样的公司,而不是让Microsemi买下Actel的这道风景!

CTO代表一家公司技术的灵魂,Xilinx今天能推出3D封装,是数年前为可持续发展而规划的成果!

饮水思源:Xilinx CTO

参考文章或注解:

[1]超越摩尔定律 赛灵思全球首发堆叠硅片互联技术(2010-10-28).http://www.eepw.com.cn/article/113995.htm )。

[2]到目前为止,FPGA 的所有工艺节点都遵循摩尔定律的发展,逻辑容量提高一倍,则成本降低一半。遗憾的是,仅仅依靠摩尔定律的发展速度,已不能满足市场对可控功耗范围内实现更多资源以及更高代工厂良率的无止境的需求。因此提出“超越摩尔定律”。

[3]http://www.semico.com/

[4]赛灵思堆叠硅片互联技术问答.http://xilinx.eetrend.com/news/1270

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。